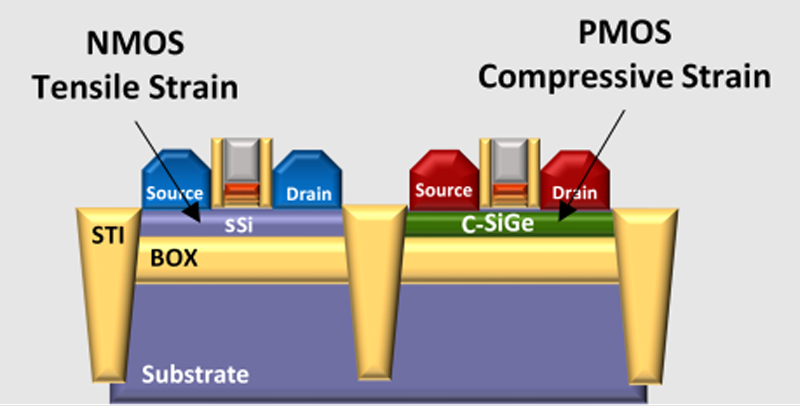

El avance en la fabricación de dispositivos FD-SOI de 10 nm implica nuevos retos, especialmente en lo referente al rendimiento y la movilidad de los portadores. Un aspecto crucial para mejorar la eficiencia en estos dispositivos es la introducción controlada de tensión en los materiales semiconductores. Esta tensión puede optimizar la movilidad de electrones en los transistores nMOS, mediante tracción, o la movilidad de huecos en los pMOS, mediante compresión. La línea piloto Fames está estudiando nuevas técnicas para potenciar el rendimiento de los próximos nodos tecnológicos, enfocándose, entre otros aspectos, en la manipulación precisa de la tensión en los materiales semiconductores, para desarrollar la próxima generación de dispositivos electrónicos basados en FD-SOI.

Las obleas sSOI (SOI con tensión incorporada) son especialmente relevantes, ya que la relajación controlada en estos materiales facilita fases posteriores como la condensación de germanio. Una de las claves está en aumentar la movilidad de los portadores en el canal de transistores de 10 nm utilizando materiales con deformación intrínseca. Para nMOS, se requiere una capa de silicio deformada por tracción, mientras que los pMOS se benefician de una capa de silicio sometida a compresión, muchas veces mediante un canal de SiGe. El uso de sustratos sSOI permite lograr estos niveles de tracción a escala de oblea.

Estos sustratos proporcionan hasta un 33% de mejora en la corriente efectiva (Ieff) para dispositivos nMOS en comparación con sustratos SOI tradicionales. Al mismo tiempo, el canal de SiGe sometido a compresión es adecuado para transistores pMOS, y se produce generalmente por técnicas de enriquecimiento de germanio.

Otro punto relevante es la proporción de germanio necesaria para conseguir canales de Ge condensado en obleas sSOI. Para alcanzar concentraciones de entre 20% y 30%, la epitaxia requiere aproximadamente un 50% de germanio, lo que puede complicar el proceso por cuestiones como el ajuste del voltaje umbral en el dispositivo final.

Relajación de la tensión de tracción

Para solucionar estos desafíos, se prioriza la relajación de la tensión de tracción antes de iniciar la condensación del germanio. En los experimentos de Fames, la amorfización de la capa delgada de silicio a través de la implantación de iones (Si o Ar), seguida de un recocido a 850°C durante 5 minutos, ha resultado efectiva para reducir la tensión de tracción y mejorar la relajación de la estructura.

Las mediciones realizadas con microscopía electrónica de transmisión y espectroscopía Raman han confirmado que la relajación de la tensión puede alcanzar hasta el 85%, permitiendo así múltiples implementaciones de los procesos de implantación y recocido para perfeccionar aún más la calidad de los sustratos sSOI.

Se prevé que futuras investigaciones continúen perfeccionando la calidad cristalina de las capas relajadas, con el objetivo de soportar el desarrollo de la próxima generación de dispositivos electrónicos basados en FD-SOI.