Un equipo de investigadores compuesto por el Instituto de Tecnología de Tokio (Tokyo Tech), la Universidad de Osaka y la Universidad de Tohoku (Japón) han desarrollado una tecnología de integración de chiplets que utilizan una tecnología denominada Pillar-Suspended Bridge (PSB). Esta tecnología cumple con los requisitos para la comunicación de chip a chip de banda ancha y la integración de chiplet escalable, con una configuración y un proceso de fabricación mínimos.

Se espera que la tecnología de integración de chiplet permita ampliar la integración y mejorar el rendimiento o reducir el consumo de energía de los dispositivos. El chiplet consiste en ensamblar sistemas principales a partir de una colección de chips de circuitos integrados que están más estrechamente acoplados que en la tecnología de empaquetado de semiconductores convencional.

La nueva tecnología desarrollada cuenta con una estructura de interconexión de puente de silicio a través de un fino MicroPillar para la comunicación de banda ancha entre chips y un proceso de fabricación llamado All Chip-last. La estructura y el proceso proporcionan los requisitos para la integración de chiplets de la forma más sencilla.

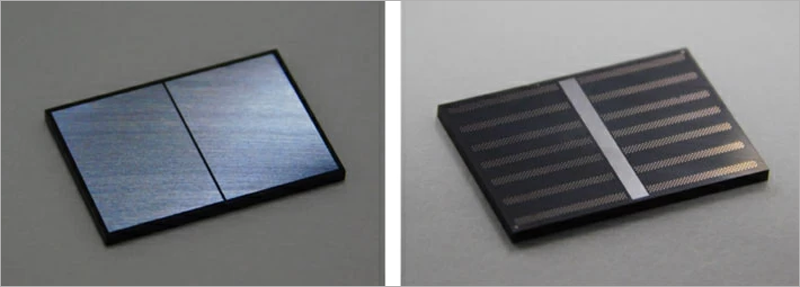

Prototipo del chiplet

Los investigadores crearon un prototipo de prueba de concepto para demostrar su viabilidad. Para ello interpusieron un metal en forma de pilar MicroPillar en la conexión entre el chiplet y el puente de silicio. Los chips se sellan con resina de molde junto con el puente y se conectan a un electrodo externo mediante un pilar alto que penetra en el molde por el lado del puente de silicio.

Esta estructura hace posible mejorar la densidad de conexión entre chips y las propiedades eléctricas al minimizar el elemento de interconexión de chiplet/puente, al tiempo que se mejora las propiedades de alta frecuencia del cableado de conexión externa y el rendimiento de disipación de calor.

Esta estructura fue creada por una alta precisión de unión y reducción del desplazamiento del troquel (fenómeno en el que el chip se mueve durante el sellado del molde) durante el proceso de fabricación con el proceso All Chip-last, y un proceso de unión con ajuste lineal de expansión (Coeficiente de Expansión Térmica: CTE).

La estructura PSB por lo tanto tiene una estructura simple y racional para la integración de chiplet utilizando un puente de silicio. Al conectar una capa de cableado con una función fan-out a esto, es posible ensamblar un paquete integrado de chiplet óptima o un sistema integrado de chiplet a gran escala.

Los investigadores esperan que esta tecnología de integración de chiplet acelere la evolución de la futura tecnología de sistemas de circuitos integrados de semiconductores en lugar de la miniaturización.